### MARINE CORPS INSTITUTE

# FUNDAMENTALS OF DIGITAL LOGIC

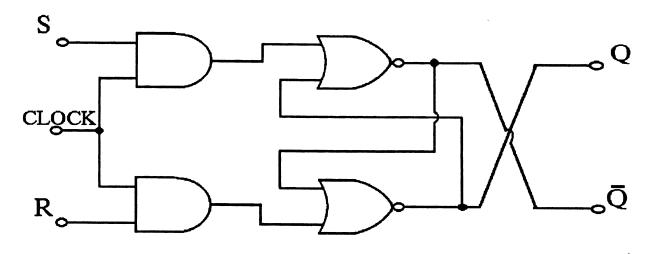

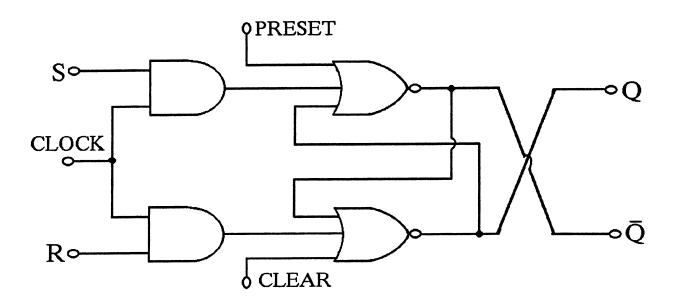

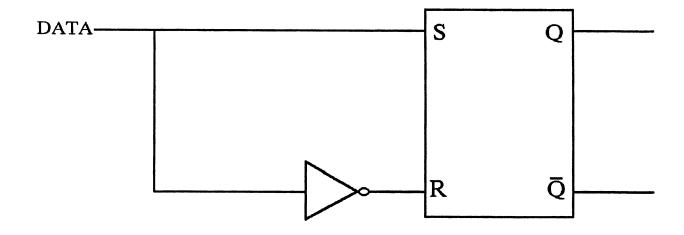

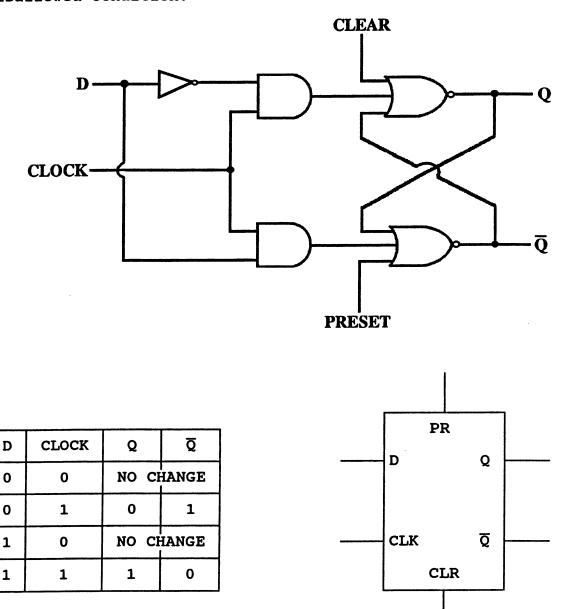

MARINE BARRACKS WASHINGTON, DC

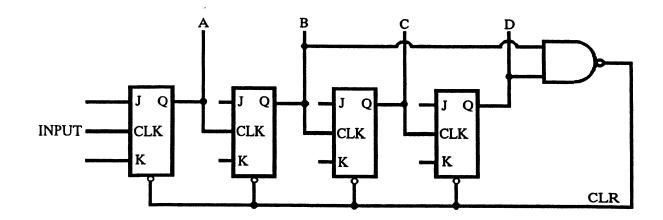

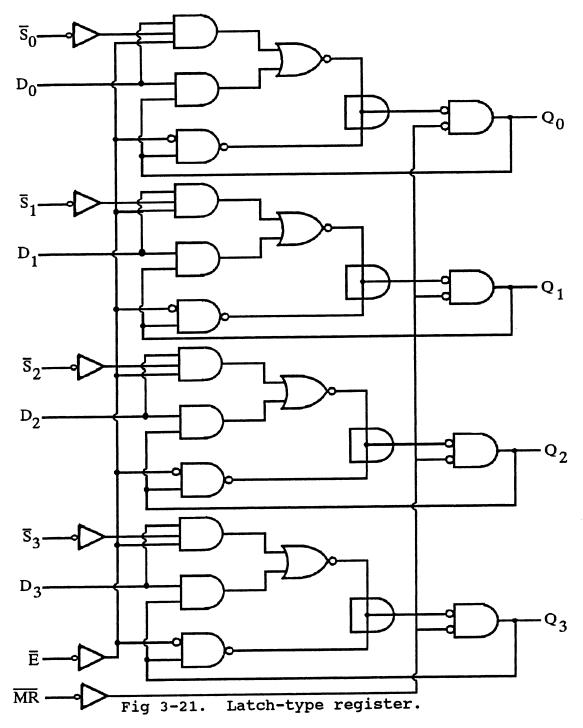

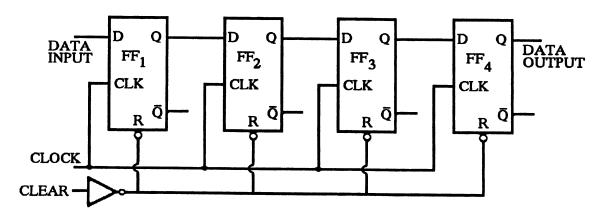

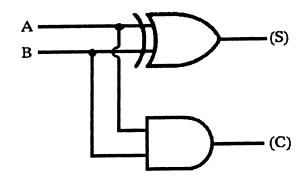

### **UNITED STATES MARINE CORPS**

MARINE CORPS INSTITUTE **WASHINGTON NAVY YARD** 912 POOR STREET SE **WASHINGTON, DC 20391-5680**

> 28.6g 16 Jan 98

### MCI 28.6g, FUNDAMENTALS OF DIGITAL LOGIC

- 1. Purpose. MCI course 28.6g, Fundamentals Of Digital Logic, is published to provide instruction to Marine electronic repairmen.

- 2. Scope. This introductory course will serve as a primer for further digital logic study. MCI 28.6g discusses numbering systems, logic operations, and basic logic diagrams. This is the foundation of the common knowledge that the electric repairman uses to base his troubleshooting decisions on.

- 3. Applicability. This course is intended for instructional purposes only. It is designed for use by Marines in the ranks of Pvt through SSgt.

- 4. Recommendations. Comments and recommendations on the contents of the course are invited and will aid in subsequent course revisions. Please complete the course evaluation questionnaire located at the end of the text and return it to:

Director (Support Team) Marine Corps Institute Washington Navy Yard 912 Poor Street SE Washington, DC 20391-5680

Lieutenant Colonel, U.S. Marine Corps

**Deputy Director**

### ERRATUM CHANGE PAGE TO COURSE MATERIAL

- 1. <u>Purpose</u>. The purpose of this change is to give the student current instructions regarding the instructions for the Review Lesson Examination page.

- 2. Action. Change the instructions found on page R-1 of this book to read as follows:

"The purpose of the review lesson examination is to prepare you for your final examination. We recommend that you try to complete your review lesson examination without referring to the text, but for those items (questions) you are unsure of, restudy the text. When you finish your review lesson and are satisfied with your responses, check your responses against the answers provided at the end of this review lesson examination.

Select the ONE answer that BEST completes the statement or that answers the item. For multiple choice items, circle your response. For matching items, place the letter of your response in the space provided."

3. This page is to be filed directly behind the Promulgation Letter of this course.

### FUNDAMENTALS OF DIGITAL LOGIC

### CONTENTS

|                   |                                                              | Page         |

|-------------------|--------------------------------------------------------------|--------------|

| Contents          |                                                              | i            |

| Student Informati | on                                                           | iii          |

| Study Guide       |                                                              | v            |

| Study Unit 1      | Binary Numbering System                                      |              |

| Lesson 1          | Numbering System Basics Exercise                             | 1-1<br>1-7   |

| Lesson 2          | Binary Mathematical Operations  Exercise                     | 1-8<br>1-22  |

| Study Unit 2      | Logic Operations                                             |              |

| Lesson 1          | Basic Logic Operations Exercise                              | 2-1<br>2-10  |

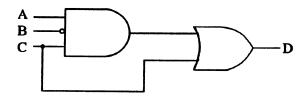

| Lesson 2          | Combinatorial Gates Exercise                                 | 2-12<br>2-19 |

| Lesson 3          | Inhibited Gates  Exercise                                    | 2-22<br>2-33 |

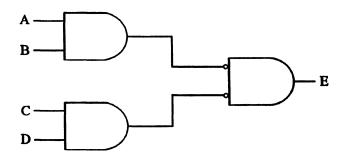

| Study Unit 3      | Common Multigate Circuits                                    | •            |

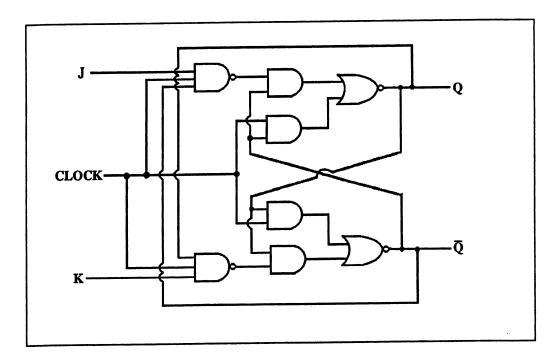

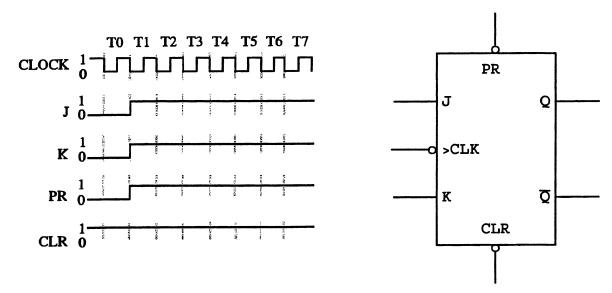

| Lesson 1          | Timing, Triggering, Clocking, and Bistable Devices  Exercise | 3-1<br>3-7   |

| Lesson 2          | Latches and Flip Flops Exercise                              | 3-9<br>3-26  |

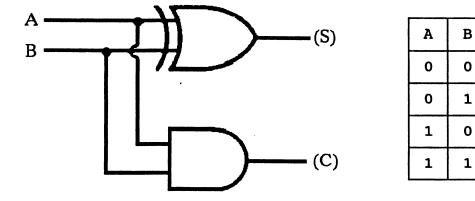

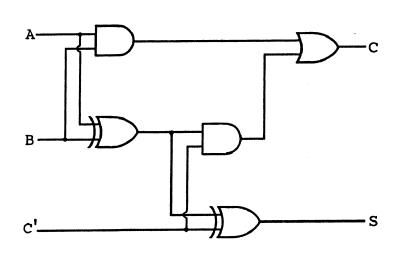

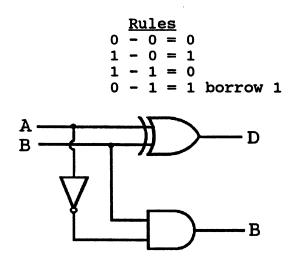

| Lesson 3          | Adders, Subtractors, Counters, and Registers  Exercise       | 3-33<br>3-46 |

| Study Unit 4      | Interpreting Digital Logic Circuits                          |              |

| Lesson 1          | The Tools of Circuit Evaluation                              | 4-1<br>4-13  |

| Lesson 2          | Circuit Evaluation Exercise                                  | 4-16<br>4-28 |

### **CONTENTS** continued

|               | Page    |

|---------------|---------|

| Review Lesson | <br>R-1 |

| Bibliography  |         |

### **Student Information**

| Number and<br>Title                    | MCI 286G<br>FUNDAMENTALS OF DIGITAL LOGIC                                                                                                                                                                                                                                        |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Study Hours                            | 10                                                                                                                                                                                                                                                                               |

| Course<br>Materials                    | Text                                                                                                                                                                                                                                                                             |

| Review Agency                          | Marine Corps Communication-Electronics School Marine Corps Air Ground Combat Center Twentynine Palms, California 92278-5020                                                                                                                                                      |

| Reserve<br>Retirement<br>Credits (RRC) | 3                                                                                                                                                                                                                                                                                |

| ACE                                    | Not applicable to civilian training/education                                                                                                                                                                                                                                    |

| Assistance                             | For administrative assistance, have your training officer or NCO log on to the MCI home page at <a href="https://www.mci.usmc.mil">www.mci.usmc.mil</a> . Marines CONUS may call toll free 1-800-MCI-USMC. Marines worldwide may call commercial (202) 685-7596 or DSN 325-7596. |

|   | - |  |

|---|---|--|

|   |   |  |

|   |   |  |

|   |   |  |

|   |   |  |

|   |   |  |

| - |   |  |

### **Study Guide**

### Congratulations

Congratulations on your enrollment in a distance education course from the Distance Learning and Technologies Department (DLTD) of the Marine Corps Institute (MCI). Since 1920, the Marine Corps Institute has been helping tens of thousands of hard-charging Marines, like you, improve their technical job performance skills through distance learning. By enrolling in this course, you have shown a desire to improve the skills you have and master new skills to enhance your job performance. The distance learning course you have chosen, MCI course 286G, Fundamentals of Digital Logic, is the foundation course of digital electronics. It is designed to be a no-tears introductory course for Marines tasked with electronic troubleshooting duties.

### Your Personal Characteristics

- YOU ARE PROPERLY MOTIVATED. You have made a positive decision to get training on your own. Self-motivation is perhaps the most important force in learning or achieving anything. Doing whatever is necessary to learn is motivation. You have it!

- YOU SEEK TO IMPROVE YOURSELF. You are enrolled to improve those skills you already possess, and to learn new skills. When you improve yourself, you improve the Corps!

- YOU HAVE THE INITIATIVE TO ACT. By acting on your own, you have shown you are a self-starter, willing to reach out for opportunities to learn and grow.

- YOU ACCEPT CHALLENGES. You have self-confidence and believe in your ability to acquire knowledge and skills. You have the self-confidence to set goals and the ability to achieve them, enabling you to meet every challenge.

- YOU ARE ABLE TO SET AND ACCOMPLISH PRACTICAL GOALS. You are willing to commit time, effort, and the resources necessary to set and accomplish your goals. These professional traits will help you successfully complete this distance learning course.

Continued on next page

### Study Guide, Continued

### Beginning Your Course

Before you actually begin this course of study, read the student information page. If you find any course materials missing, notify your training officer or training NCO. If you have all the required materials, you are ready to begin.

To begin your course of study, familiarize yourself with the structure of the course text. One way to do this is to read the table of contents. Notice the table of contents covers specific areas of study and the order in which they are presented. You will find the text divided into several study units. Each study unit is comprised of two or more lessons, lesson exercises, and finally, a study unit exercise.

## Leafing Through the Text

Leaf through the text and look at the course. Read a few lesson exercise questions to get an idea of the type of material in the course. If the course has additional study aids, such as a handbook or plotting board, familiarize yourself with them.

### The First Study Unit

Turn to the first page of study unit 1. On this page, you will find an introduction to the study unit and generally the first study unit lesson. Study unit lessons contain learning objectives, lesson text, and exercises.

# Reading the Learning Objectives

Learning objectives describe in concise terms what the successful learner, you, will be able to do as a result of mastering the content of the lesson text. Read the objectives for each lesson and then read the lesson text. As you read the lesson text, make notes on the points you feel are important.

### Completing the Exercises

To determine your mastery of the learning objectives and text, complete the exercises developed for you. Exercises are located at the end of each lesson, and at the end of each study unit. Without referring to the text, complete the exercise questions and then check your responses against those provided.

Continued on next pa

### Study Guide, Continued

### Continuing to March

Continue on to the next lesson, repeating the above process until you have completed all lessons in the study unit. Follow the same procedures for each study unit in the course.

### Preparing for the Final Exam

To prepare for your final exam, you must review what you learned in the course. The following suggestions will help make the review interesting and challenging.

- CHALLENGE YOURSELF. Try to recall the entire learning sequence without referring to the text. Can you do it? Now look back at the text to see if you have left anything out. This review should be interesting. Undoubtedly, you'll find you were not able to recall everything. But with a little effort, you'll be able to recall a great deal of the information.

- USE UNUSED MINUTES. Use your spare moments to review. Read your notes or a part of a study unit, rework exercise items, review again; you can do many of these things during the unused minutes of every day.

- APPLY WHAT YOU HAVE LEARNED. It is always best to use the skill or knowledge you've learned as soon as possible. If it isn't possible to actually use the skill or knowledge, at least try to imagine a situation in which you would apply this learning. For example make up and solve your own problems. Or, better still, make up and solve problems that use most of the elements of a study unit.

- USE THE "SHAKEDOWN CRUISE" TECHNIQUE. Ask another Marine to lend a hand by asking you questions about the course. Choose a particular study unit and let your buddy "fire away." This technique can be interesting and challenging for both of you!

- MAKE REVIEWS FUN AND BENEFICIAL. Reviews are good habits that enhance learning. They don't have to be long and tedious. In fact, some learners find short reviews conducted more often prove more beneficial.

Continued on next page

### Study Guide, Continued

### Tackling the Final Exam

When you have completed your study of the course material and are confident with the results attained on your study unit exercises, take the sealed envelope marked "FINAL EXAM" to your unit training NCO or training officer. Your training NCO or officer will administer the final examination and return the examination and the answer sheet to MCI for grading. Before taking your final examination, read the directions on the DP-37 answer sheet carefully.

### Completing Your Course

The sooner you complete your course, the sooner you can better yourself by applying what you've learned! HOWEVER--you do have 2 years from the date of enrollment to complete this course.

### **Graduating!**

As a graduate of this distance education course and as a dedicated Marine, your job performance skills will improve, benefiting you, your unit, and the Marine Corps.

Semper Fidelis!

#### STUDY UNIT 1

#### BINARY NUMBERING SYSTEM

Introduction. A numbering system provides the framework in which we represent numerical quantities as well as perform mathematical computations. The numbering system we are most familiar with is a positional numbering system, the decimal system. This system uses the Arabic numerals 0, 1, 2, 3, 4, 5, 6, 7, 8, and 9. These numerals are also known as symbols or digits. While some systems may use more than just these ten symbols and others less, the system we will study in this course, the binary system, uses only two symbols. The binary numbering system is the heart of digital logic. You must understand the binary numbering system if you are to successfully troubleshoot digital electronic equipment.

### Lesson 1. NUMBERING SYSTEM BASICS

### LEARNING OBJECTIVES

- Identify in writing the three components of a positional numbering system.

- Given the base of a numbering system, select the maximum number of digits that system contains.

- 3. Determine the base of any given number in a positional numbering system.

- 4. State in writing the base of a numbering system that uses two digits.

- 5. Given the base of any three-digit number, determine the place value for each digit.

### 1101. Base, Point, and Place Value

The positional numbering system you encounter daily is the base ten numbering system. What makes this system the base ten system? What makes this system a positional system? As you learn to answer these questions, you'll learn the basics of all numbering systems and be able to apply this knowledge to help you understand the binary numbering system. Let's take a closer look at numbers. Basically (at least for the purposes of this course) there are three parts to every number: base or radix, point, and place value. The following explains these three parts.

a. <u>Base</u>. The base or radix is the logical place to begin to explain a numbering system—as this is what a positional numbering system is built on.

- (1) The base of a number determines the number of symbols in that system. For example, the decimal system, base ten, uses ten digits: 1, 2, 3, 4, 5, 6, 7, 8, 9, and 0. The octal numbering system, base eight, uses eight digits: 1, 2, 3, 4, 5, 6, 7, and 0. How many digits are used in the binary, base two, numbering system? That's right, two--1 and 0. Remember, digits, symbols, and numerals have the same meaning in this context.

- (2) Within a numbering system, no single digit can represent a quantity equivalent to or higher than its base. Notice that there is no digit higher than 7 in base eight, no digit higher than 9 in base 10, etc. This will be explained later in the text.

- (3) The base of a number when shown is written as a subscript to that number. For example, the number 18<sub>10</sub> is read "one eight base ten." Normally the base will not be shown for a base 10 number. If no base is shown, assume base 10. This number 72<sub>9</sub> would be read "seven two base nine." Okay, now it's your turn. How would you read the number 23<sub>6</sub>? If you said, "two three base six", you're right. We'll look at one more and then go on. How would you read the number 514? Couldn't fool you? Yes, this number is read "five one four base ten" or simply five hundred fourteen. Remember, if no base is stated, assume base ten.

- (4) The base also allows you to know the place value for each digit, another concept which you will learn in this lesson.

Okay, now it's time to see what you've learned--what does the base tell you about a number?

Your answer should have included the following points:

- The base determines the number of digits used in that system.

- No single digit represents a quantity higher than or equivalent to the base.

- The base allows you to determine place value for each digit.

- b. <u>Point</u>. The point of a numbering system divides whole numbers from fractions and takes the name of the system that it is in. As an example, the point in the decimal system is known as the decimal point, something you're sure to be familiar with. Looking at the decimal (base ten) number 134.75, whole numbers are always to the left of the point (in this case--decimal point) and fractions are always to the right of the point. In the binary number 101.112 the same relationship exists--whole numbers to the left, and fractions to the right of the binary point. Examples of points for other systems are the ternary point (base three), the octal point (base eight), and so on.

- c. <u>Place value</u>. Place value describes the space (or location) that a number resides in. Just as every numeral has a value, every position in which a digit is placed also has a value.

- (1) Let's look at the decimal number 105.0. Starting at the decimal point and going left, the first digit of this number tells you how many ones are in that number, the second how many tens, the third how many hundreds. The digit to the right of the decimal tells you how many tenths the number contains. Notice that the 0 serves as a place holder; that is, the 0 has no numerical value but simply allows the 1 and the 5 to maintain their proper place. Exploring further, you can see that each place is a power of the base. This means that (for base ten) starting at the decimal point and going left—the first place is 10° or ones, the second place is 10° or tens, the third place 10° or one hundreds, while the place to the right of the decimal point is 10° or tenths (fig 1-1).

| 104   | 10 <sup>3</sup> | 10 <sup>2</sup> | 10 <sup>1</sup> | 10 <sup>0</sup> | 10-1 |

|-------|-----------------|-----------------|-----------------|-----------------|------|

| 10000 | 1000            | 100             | 10              | 1               | .1   |

Fig 1-1. Place values for base ten.

A quick review of exponents (powers): The exponent is written as a superscript to the number ( $N^{power}$ ). The power tells you how many times to multiply the number by itself. As an example,  $N^3$  means  $N \times N \times N$  and is read N raised to the third power or simply N to the third power.  $N^2$  means  $N \times N$  and is read N to the second power. Further, any number raised to the zero power equals 1 ( $N^0$  = 1) and any number raised to the first power equals that number ( $N^1$  = N). Negative exponents in this form  $N^{-x}$  mean  $1/N^x$ . As an example,  $5^{-2}$  (read five to the negative second power), equals  $1/5^2$  or 1/25 ( $1/\{5 \times 5\}$ ).

This type of relationship, which exists for all numbering systems, can be seen in table 1-1. As an example, using the point as reference and going left, the place values for the first few places in base three are  $1(3^0)$ ,  $3(3^1)$ ,  $9(3^2)$ , and  $27(3^3)$ ; in base five  $1(5^0)$ ,  $5(5^1)$ ,  $25(5^2)$ , and  $125(5^3)$ . In table 1-1 you can also see the place values for other numbering systems with base 2 (binary numbering system) highlighted.

(2) The pattern found to the left of the point is also found to the right. However, place values to the right of the point are fractional values. The difference is simply that powers of the base to the right of the point are negative powers. This is illustrated in the number 25.817. The place values, starting at the decimal point and going left, would be 100 and 101; then from the point and to the right, 10-1, 10-2, and 10-3.

Accordingly, in the number 111.01, the digits to the left of the binary point represent whole numbers while those to the right of the point represent fractions.

What is the place value that each of these digits holds (in order from left to right)?

If you said  $2^2$ ,  $2^1$ ,  $2^0$ ,  $2^{-1}$ , and  $2^{-2}$ , you're right.

Table 1-1 shows examples of place values in other bases.

Table 1-1. Place Values For Bases Two Through Ten

| Binary:                                | (Base  | Two)                   |                       |                        |                       |                     |                         |                         |

|----------------------------------------|--------|------------------------|-----------------------|------------------------|-----------------------|---------------------|-------------------------|-------------------------|

| base <sup>power</sup><br>equivalent v  | alue   | 2 <sup>4</sup><br>16   |                       | 2 <sup>2</sup>         | 2 <sup>1</sup>        |                     | 2 <sup>-1</sup>         |                         |

| Ternary:                               | (Base  | Three                  | <b>:)</b>             |                        |                       |                     |                         |                         |

| base <sup>power</sup><br>equivalent v  | alue   | 3 <sup>4</sup><br>81   | -                     | 3 <sup>2</sup><br>9    | 3 <sup>1</sup><br>3   | 3 <sup>0</sup>      |                         | -                       |

| Quaternary:                            | (Base  | Four)                  |                       |                        |                       |                     |                         |                         |

| base <sup>power</sup><br>equivalent v  | alue   | 44<br>256              |                       |                        | 4 <sup>1</sup><br>4   | 4 <sup>0</sup>      |                         | _                       |

| Quinary:                               | (Base  | Five)                  |                       |                        |                       |                     |                         |                         |

| base <sup>power</sup><br>equivalent v  |        | _                      | _                     | 5 <sup>2</sup><br>25   | 5 <sup>1</sup>        | 5 <sup>0</sup><br>1 | 5 <sup>-1</sup>         | 5 <sup>-2</sup>         |

| Senary:                                | (Base  | Six)                   |                       |                        |                       |                     |                         |                         |

| base <sup>power</sup><br>equivalent v  | alue   | 6 <sup>4</sup><br>1296 |                       | 6 <sup>2</sup><br>36   | 6 <sup>1</sup>        | 6 <sup>0</sup><br>1 | 6 <sup>-1</sup><br>.17  |                         |

| Septenary:                             | (Base  | Sever                  | n)                    |                        |                       |                     |                         |                         |

| base <sup>power</sup><br>equivalent v  |        | •                      | •                     | 7 <sup>2</sup><br>49   | 7 <sup>1</sup><br>7   | 7 <sup>0</sup><br>1 | 7 <sup>-1</sup>         | 7 <sup>-2</sup><br>.02  |

| Octonary:                              | (Base  | Eight                  | :)                    |                        |                       |                     |                         |                         |

| base <sup>power</sup><br>equivalent v  | alue . | 8 <sup>4</sup><br>4096 | _                     | 8 <sup>2</sup><br>64   | 8 <sup>1</sup>        | 8 <sup>0</sup><br>1 | 8 <sup>-1</sup><br>.125 | -                       |

| Nonary:                                | (Base  | Nine)                  |                       |                        |                       |                     |                         |                         |

| base <sup>power</sup><br>equivalent va | alue   | 94<br>6561             | 9 <sup>3</sup><br>729 | 9 <sup>2</sup><br>81   | 9 <sup>1</sup><br>9   | 9 <sup>0</sup><br>1 | 9 <sup>-1</sup>         | 9 <sup>-2</sup><br>.012 |

| Decimal:                               | (Base  | Ten)                   |                       |                        |                       |                     |                         |                         |

| base <sup>power</sup><br>equivalent va | .l 1   | 104                    |                       | 10 <sup>2</sup><br>100 | 10 <sup>1</sup><br>10 | 100                 | 10-1                    | 10 <sup>-2</sup><br>.01 |

### 1102. Binary Numbers

Now that you know the basics of a positional numbering system, it's time to concentrate on binary numbers. A knowledge of other numbering systems may be helpful when troubleshooting some digital equipment, but a basic understanding of the fundamentals of binary will help you go a long way in understanding any system.

- a. <u>Common characteristics</u>. Looking closely at the binary system, you see that it is no different in structure than the numbering systems we've already looked at. Just as there is no single digit in base ten to represent the quantity ten, there is no single digit in base two to represent the quantity two. All positional numbering systems share this same characteristic. So in the binary system there are just ones and zeros. Any system with only two digits has to be easy!

- b. <u>Application</u>. Let's look at a binary number to see if you understand them as well as you think. Using the binary number 1011.0 you should be able to apply the basics of what you've learned so far.

Note: This number has no subscript, but for the purposes of this course, consider it a binary number. The dropping of the subscript is a convention used for ease of reading that will be employed in this text when numbers of different numbering systems are not mixed.

So, getting back to your number (1011.0)... we know the base is two; the place values are  $2^0$ ,  $2^1$ ,  $2^2$ ,  $2^3$ , and  $2^{-1}$ , and that the point is the binary point.

| 23 | 2 <sup>2</sup> | 21 | 20 | 2-1 |

|----|----------------|----|----|-----|

| 1  | 0              | 1  | 1  | .0  |

(1) Going further, it is easy to see the value of each digit. The highlighted digit in 1011.0 is in the 2³ position, so to find the value of that digit we could multiply the digit by the place value of its position. Simply put, this highlighted digit 1011.0 would mean 1 x 2³ or 8. The next digit 1011.0 means 0 x 2² or 0. The next digit, 1011.0, means 1 x 2¹ or 2. The last whole number digit, 1011.0, means 1 x 2⁰ or 1. The digit representing a fractional value 1011.0 means 0 x 2⁻¹ or 0.

Your turn again: What are the place values and the value of each of the digits in  $11101.0_2$ ? (Table 1-1 may help.)

| Yours answers should resemble these: |             |    |                    |                                   |  |  |  |

|--------------------------------------|-------------|----|--------------------|-----------------------------------|--|--|--|

| 1101.0 <sub>2</sub>                  | place value | 16 | (24)               | digit value 1 x 24 or 16          |  |  |  |

| 11101.02                             | place value | 8  | (2 <sup>3</sup> )  | digit value 1 x $2^3$ or 8        |  |  |  |

| 11101.02                             | place value | 4  | (2 <sup>2</sup> )  | digit value 1 x $2^2$ or 4        |  |  |  |

| 11101.02                             | place value | 2  | (2 <sup>1</sup> )  | digit value $0 \times 2^1$ or $0$ |  |  |  |

| 1110 .02                             | place value | 1  | (2 <sup>0</sup> )  | digit value 1 x $2^0$ or 1        |  |  |  |

| 11101.02                             | place value | .5 | (2 <sup>-1</sup> ) | digit value 0 x $2^{-1}$ or 0     |  |  |  |

(2) Determining these values in the binary numbering system is relatively easy to do because of the small number of digits (ones or zeros) that you would find in each position. Of course this concept holds true for all positional numbering sytems; there are just larger numbers to deal with. This way of looking at numbers will be helpful when we try to convert from one system to another.

<u>Lesson Summary</u>. This lesson introduced you to positional numbering systems. The emphasis on base two will help, not only as you complete this course, but as you troubleshoot electronic equipment.

Exercise: Complete items 1 through 6 by performing the action required. Check your responses against those listed at the end of this study unit.

- 1. The number  $10_{10}$  may be read as one zero base

- a. two.

c. ten.

b. eight.

d. sixteen.

- 2. What is the maximum number of different digits used in the base eight numbering system?

- a. Seven

c. Nine

b. Eight

d. Sixteen

- 3. What numbering system uses only two digits?

- a. Binary

c. Octal

b. Quinary

d. Decimal

- 4. The place value for each digit of 1102 in order from left to right is

- a. eight, four, two. c. four, two, one.

- b. eight, four, one. d. four, two, zero.

- 5. The three parts to the binary numbering system are \_\_\_\_\_\_\_, and \_\_\_\_\_\_\_.

- 6. In the binary system the separates fractions from whole numbers.

#### Lesson 2. BINARY MATHEMATICAL OPERATIONS

### LEARNING OBJECTIVES

- 1. Given any binary number, select the decimal equivalent for that number.

- 2. Given any decimal number, select the binary equivalent for that number.

- 3. Given any single-digit two-term binary multiplication problem, state the solution in writing.

- 4. Given any single-digit two-term binary subtraction problem, state the solution in writing.

- 5. Given any single-digit two-term binary addition problem, state in writing the solution.

#### 1201. Binary to Decimal Conversion

There are more than a few ways to convert binary to decimal. We will concentrate on the easiest method. Learning to convert numbers from one base to another is more than just a mathematical exercise. The purpose of conversion is to aid you in troubleshooting digital equipment.

- a. <u>Basics</u>. First let's look at the binary number 152.0. If you said that can't be a binary number, again you're right. The largest digit in binary is 1, so, of course, 152.0 can't be a binary number. So, going over what we know of the binary system, we can see that the...

- (1) ... <u>base</u> is two; as is the radix--remember base and radix are the same.

- (2) ... <u>point</u> is the binary point and divides the fractional part of the number from the whole numbers.

- (3) ... place value is a function of the powers of the base. Put another way, place value can be easily determined by using the point as a reference. Going left from the point, the first place value is the base raised to the zero power, the next place is the base raised to the first power, the next place is the base raised to the second power, and so on. Going right from the point, the first place is the base raised to the negative first power, the next place is the base raised to the negative second power, the third place would be the base raised to the negative third power, and so on.

- b. <u>Digit values</u>. Now try the decimal number 152.0. Starting at the decimal point and going left, look at the place values  $10^0$ ,  $10^1$ , and  $10^2$ . There is one place to the right of the decimal point and that is  $10^{-1}$ . These values are the same as ones, tens, and hundreds going left and tenths going right. Now look at the value of the digits. THESE VALUES WOULD BE THE DIGIT MULTIPLIED BY THE PLACE VALUE THE DIGIT IS IN. The following box illustrates this:

| Digi | t | Place Value            | Digit Value |

|------|---|------------------------|-------------|

| 1    | x | 10 <sup>2</sup> or 100 | 100         |

| 5    | × | 10 <sup>1</sup> or 10  | 50          |

| 2    | × | 10 <sup>0</sup> or 1   | 2           |

| 0    | x | 10 <sup>-1</sup> or .1 | 0           |

Now if you were to add the values of the digits, you'd find you had the value of the number. In other words, 100 + 50 + 2 + 0 = 152. Now we'll apply this to binary numbers.

- c. Applications. Okay, let's look at the binary number 1101.0, and apply this same concept.

- (1) A look at the place values from the binary point left shows a one (2<sup>0</sup>), a two (2<sup>1</sup>), a four (2<sup>2</sup>), and an eight (2<sup>3</sup>). From the binary point right we have .5 (2<sup>-1</sup>). If you now look at the digit values (place value times digit) in this same order (binary point and left) you would have one, zero, four, eight, and zero. This is illustrated as follows:

| Dig | Digit |                    | ue  | Digit Value |

|-----|-------|--------------------|-----|-------------|

| 1   | x     | 2 <sup>3</sup> or  | 8   | 8           |

| 1   | x     | 2 <sup>2</sup> or  | 4   | 4           |

| o   | ×     | 2 <sup>1</sup> or  | 2   | 0           |

| 1   | ×     | 20 or              | 1   | 1           |

| 0   | ×     | 2 <sup>-1</sup> or | . 5 | 0           |

- (2) If you again add the digit values, you'll find you have the value of the number, 8 + 4 + 0 + 1 + 0 = 13. Not only do you have the value of the number, but you've converted a binary number to a decimal number. As you can see, it's easy.

- (3) If we use a chart similar to this one, this is seen somewhat easier.

| 24 | 23 | 22 | 21 | 20 | 2-1 | 2-2 | 2-3  |

|----|----|----|----|----|-----|-----|------|

| 16 | 8  | 4  | 2  | 1  | .5  | .25 | .125 |

The chart above is similar to the one in lesson one. If we put our number 1101.0 on the bottom of the chart in proper place value--

| 24 | 23 | 22  | 21  | 20  | 2-  | 1 2-2 | 2-3  |   |    |

|----|----|-----|-----|-----|-----|-------|------|---|----|

| 16 | 8  | 4   | 2   | 1   | .5  | .25   | .125 | _ |    |

|    | 1  | 1   | 0   | 1   | 0   |       |      |   |    |

|    | 8  | + 4 | + 0 | + 1 | + 0 |       |      | = | 13 |

--as shown it is easy to discern the decimal value of the binary number 1101.0. Looking at two more binary numbers 11111.1 and 1001.01, it's easy to see the decimal equivalents, once the binary numbers are placed on the following charts:

| 24 | 23  | 2 <sup>2</sup> | 21  | 20  | 2-  | 1 2-2 | 2-3    |

|----|-----|----------------|-----|-----|-----|-------|--------|

|    |     |                |     |     |     | .25   |        |

|    | 1   | 0              | 0   | 1   | 0   | 1     |        |

|    | 8 - | <b>+</b> 0     | + 0 | + 1 | + 0 | + .25 | = 9.25 |

(4) Now you try these two binary numbers, 10000.11 and 10101.01 on your own. You can use the two blank charts provided if you wish.

| 2 <sup>4</sup> | 2 <sup>3</sup> | 2 <sup>2</sup> | 2 <sup>1</sup> | 2 <sup>0</sup> | 2 <sup>-1</sup> | 2 <sup>-2</sup> | 2 <sup>-3</sup>         |

|----------------|----------------|----------------|----------------|----------------|-----------------|-----------------|-------------------------|

| 16             | 8              | 4              |                | 1              | .5              | .25             | .125                    |

|                |                |                |                |                |                 |                 | 2 <sup>-3</sup><br>.125 |

You should have gotten 16.75 and 21.25 as the decimal equivalents. If you used the charts to convert, they should have looked like the two that follow:

| 2 <sup>4</sup><br>16 |   | 2 <sup>3</sup><br>8 |   | 2 <sup>2</sup><br>4 |   | 2 <sup>1</sup> |   | 2 <sup>0</sup><br>1 |   | 2 <sup>-1</sup> | • | 2 <sup>-2</sup><br>25 | 2 <sup>-3</sup><br>.125 |   |       |

|----------------------|---|---------------------|---|---------------------|---|----------------|---|---------------------|---|-----------------|---|-----------------------|-------------------------|---|-------|

| 1                    |   | 0                   |   | 0                   |   | 0              |   | 0                   |   | 1               |   | 1                     |                         |   |       |

| 16                   | + | 0                   | + | 0                   | + | 0              | + | 0                   | + | .5              | + | .25                   |                         | = | 16.75 |

| 2 <sup>4</sup><br>16 |   | 2 <sup>3</sup>      |   | 2 <sup>2</sup><br>4 |   | 2 <sup>1</sup> |   | 2 <sup>0</sup>      |   | 2 <sup>-1</sup> |   | 2 <sup>-2</sup><br>25 | 2 <sup>-3</sup><br>.125 |   |       |

| 1                    |   | 0                   |   | 1                   |   | 0              |   | 1                   |   | 0               |   | 1                     |                         |   |       |

| 16                   | + | 0                   | + | 4                   | + | 0              | + | 1                   | + | 0               | + | .25                   |                         | = | 21.25 |

If you didn't get the answers above, you need to review the study unit up to this point. At any rate, try one more conversion: what is the decimal equivalent of this binary number 10111.101? Converting from binary to decimal is easy in this manner. The following perforated pages can be pulled out for use in conversions on the job. By the way, did you get 23.625 as the answer to that last problem?

(This page intentionally left blank.)

(5) Pull out conversion charts.

| 24          | 23  | 22               | 21       | 20           | 2-1                   | 2-2         | 2-3   |

|-------------|-----|------------------|----------|--------------|-----------------------|-------------|-------|

| 16          | 8   | <b>2</b>         | 2        | 1            | . 5                   | . 25        | .125  |

|             |     |                  |          |              |                       |             |       |

| _           | _   | _                | _        | _            | _                     | _           | _     |

| 24          | 23  | . 2 <sup>2</sup> | 21       | 20           | 2-1                   | 2-2         | 2-3   |

| <u>16</u>   | 8   | 44               | 2        | 1            | 2 <sup>-1</sup>       | .25         | .125  |

|             |     |                  |          |              |                       |             |       |

| 24          | 23  | 22               | 21       | 20           | 2 <sup>-1</sup><br>.5 | 2-2         | 2-3   |

| 16          | 8   | - 4              | 2        | 1            | .5                    | .25         | .125  |

|             |     |                  |          |              |                       |             |       |

| - 4         | - 3 | - 2              | -1       | -0           | 2-1                   | 2           | a 2   |

| 24          | 23  | 22               | 21       | 20           | 2-1                   | 2-2         | 2-3   |

| 16          | 8   | 4                |          |              | .5                    | .25         | .125  |

|             |     |                  |          |              |                       |             |       |

| 24          | 23  | 22               | 21       | 20           | 2 <sup>-1</sup><br>.5 | 2-2         | 2-3   |

| 16          | 8   | 44               | 2        | 1            | .5                    | .25         | .125  |

|             |     |                  |          |              |                       |             |       |

| 24          | 23  | 2                | 21       | 20           | 2-1                   | 2-2         | 2-3   |

| 16          | 25  | 2-<br>A          | 2-       | 1            | 2 <sup>-1</sup><br>.5 | 2 -<br>25   | 125   |

| 10          |     |                  |          | <del>_</del> |                       | . 23        | . 123 |

|             |     | _                |          |              |                       |             |       |

| 24          | 23  | 2 <sup>2</sup>   | 21       | 20           | 2-1                   | 2-2         | 2-3   |

| <u>16</u>   | 8   | 4                | 2        | 1            | 2 <sup>-1</sup>       | .25         | .125  |

|             |     |                  |          |              | •                     |             |       |

| 24          | 23  | 22               | 21       | 20           | 2-1                   | 2-2         | 2-3   |

| <b>1</b> 6  | . 8 | - 4              | 2        | 1            | .5                    | .25         | .125  |

| <del></del> |     |                  |          |              |                       |             |       |

| _           | _   | •                |          | •            |                       | _           | _     |

| 24          | 23  | 22               | 21       | 20           | 2-1                   | 2-2         | 2-3   |

| 16          | 8   | 4                | 2        | 1_           | .5                    | .25         | .125  |

|             |     |                  |          |              |                       |             |       |

| 24          | 23  | 22               | 21       | 20           | 2-1                   | 2-2         | 2-3   |

|             | 8   | 4                |          |              |                       |             |       |

|             |     |                  |          |              |                       |             |       |

| -1          | 23  | -2               | 21       | 20           | 2-1                   | 2-2         | 2-3   |

|             |     |                  |          |              |                       |             |       |

| 10          | - 0 | 4                | <u> </u> | <del>_</del> | .5                    | .25         | .125  |

|             |     |                  |          |              |                       |             |       |

| 24          | 23  | 2 <sup>2</sup>   | 21       | 20           | 2-1                   | 2-2         | 2-3   |

| 16          | 8   | 4                | 2        | 1            | .5                    | .25         | .125  |

|             |     |                  |          |              |                       |             |       |

| 24          | 23  | 22               | 21       | 20           | 2-1                   | 2-2         | 2-3   |

| 16          |     |                  |          | _            | .5                    | <del></del> | _     |

| 10          | 0   |                  | <u> </u> | Т            |                       | . 23        | .123  |

| 24          | 23          | 22             | 21          | 20 | 2-1 | 2-2 | 2-3  |

|-------------|-------------|----------------|-------------|----|-----|-----|------|

|             |             |                |             |    |     |     | .125 |

|             |             |                |             |    |     |     |      |

|             |             | - 2            | -1          | -0 | 2-1 | 2-2 | 2-3  |

| 24          | 23          | 22             | 21          | 20 | 2-1 | 2-2 | 125  |

| 16          | 8           | 4              |             |    | .5  | .23 | .125 |

|             |             |                |             |    |     |     |      |

| 24          | 23          | 2 <sup>2</sup> | 21          | 20 | 2-1 | 2-2 | 2-3  |

|             |             |                |             |    | . 5 |     |      |

|             |             |                |             |    |     |     |      |

| -1          | .3          | 22             | 21          | 20 | 2-1 | 2-2 | 2-3  |

|             |             |                |             |    | .5  |     | _    |

| 10          | 0           |                |             |    |     |     |      |

|             |             |                |             |    |     | _   | _    |

| 24          | 23          | 2 <sup>2</sup> | 21          | 20 | 2-1 | 2-2 | 2-3  |

| 16          | 8           | 4              | 2           | 1  | .5  | .25 | .125 |

|             |             |                |             |    |     |     |      |

| 24          | 23          | 22             | 21          | 20 | 2-1 | 2-2 | 2-3  |

| 16          | 2°<br>8     | 4              | 2           | 1  | .5  | .25 | .125 |

| <del></del> | <del></del> |                |             |    |     |     |      |

|             | _           |                |             | •  | . 1 | - 2 | 3    |

| 24          |             | 22             |             |    | 2-1 |     |      |

| <u>16</u>   | 8           | 44             | 2           | 1  | .5  | .25 | .125 |

|             |             |                |             |    |     |     |      |

| 24          | 23          | 22             | 21          | 20 | 2-1 | 2-2 | 2-3  |

| _           |             |                |             |    | .5  |     |      |

|             |             |                |             |    |     |     |      |

|             | •           | 2              | -1          | -0 | 0-1 | 0=2 | 2-3  |

|             |             |                |             |    | 2-1 |     | _    |

| 16          | 8           | 4              |             |    | .5  | .25 | .125 |

|             |             |                |             |    |     |     |      |

| 24          | 23          | 2 <sup>2</sup> | 21          | 20 | 2-1 | 2-2 | 2-3  |

| 16          |             |                |             |    | .5  |     |      |

|             |             |                |             |    |     |     |      |

| -4          | <b>~</b> 3  | 22             | 21          | 20 | 2-1 | 2-2 | 2-3  |

| 24<br>16    |             |                |             |    | .5  |     |      |

| 10          |             | <u></u>        |             |    |     |     |      |

|             |             |                |             |    |     | _   | _    |

| 24          |             |                |             |    | 2-1 |     |      |

| 16          | 88          | 4              | 2           | 1  | .5  | .25 | .125 |

|             |             |                |             |    |     |     |      |

| 24          | 23          | 2 <sup>2</sup> | 21          | 20 | 2-1 | 2-2 | 2-3  |

| 16          |             |                |             |    | .5  |     |      |

| <u> </u>    |             |                | <del></del> | *  |     |     |      |

|             | _           | _              | _           | _  | •   | - 0 | 3    |

| 24          | _           | 2 <sup>2</sup> |             |    | 2-1 |     |      |

| 16          | 88          | 4              | 2           | 1  | .5  | .25 | .125 |

### 1202. Decimal to Binary Conversion

As with converting binary to decimal, there are different methods of converting decimal to binary. The method you will use will be straightforward, simple, and based on the skills you've acquired in this text.

- a. <u>Subtraction method</u>. As you might expect, place value and digit value are the determinants in this conversion process as they were in the previous process. The subtraction method is easy to use because the base is so small in the binary numbering system. Again the use of the previously introduced handy chart will prove helpful. The conversion is accomplished in three steps.

- (1) Steps. This is a simple three step-method:

| STEP | SUBTRACTION METHOD                                                                                    |

|------|-------------------------------------------------------------------------------------------------------|

| 1    | Determine the largest binary place value that can be subtracted from the decimal you want to convert. |

| 2    | Subtract the base two place value from the decimal number.                                            |

| 3    | If there is a remainder, repeat the first two steps until the desired accuracy is reached.            |

It is during step one that the digits of your new number will be determined. Each successive place value that can be subtracted from the decimal number will be a 1 in the new number, and each place value that is skipped will be a 0.

(2) Examples. Examples of this method will make it easier to see. It's time again for that famous chart so you can see the place values easily.

| 24 | 23 | 2 <sup>2</sup> | 21 | 20 | 2-1 | 2-2 | 2-3  |

|----|----|----------------|----|----|-----|-----|------|

| 16 | 8  | 4              | 2  | 11 | . 5 | .25 | .125 |

Let's try lucky 13 as our first decimal number to convert to binary. Step one tells you to determine the largest binary place value you can subtract from the decimal number. The number  $2^4$ , or 16, is too big to subtract from 13, but  $2^3$ , or 8, the next place value will work. A 1 goes in the  $2^3$  or 8 place value column—this is the first digit of the binary number.

| 24 | 23 | 22 | 21 | 20 | 2-1 | 2-2 | 2-3  |

|----|----|----|----|----|-----|-----|------|

| 16 | 88 | 4  | 2  | 1  | . 5 | .25 | .125 |

|    | 1  |    |    |    |     |     |      |

Our next step is to subtract the selected number (large binary place value that could be subtracted), thus 13 - 8 = 5. The final step is to repeat the first two steps if there is a remainder. Since we have a remaind of 5 in this example, it's time to look for the largest place value that we can subtract from 5 (step one) and subtract it (step two). It looks as though  $2^2$  or 4 "ha the duty." A 1 goes in the  $2^2$  or 4 place value column—the second digit of the new number.

| 24 | 23 | 2 <sup>2</sup> | 21 | 20 | 2-1 | 2-2 | 2-3  |

|----|----|----------------|----|----|-----|-----|------|

| 16 | 88 | 4              | 2  | 1  | . 5 | .25 | .125 |

|    | 1  | 1              |    |    |     |     |      |

Subtracting again gives us 5-4=1. Step three tells us what to do with a remainder--go to step one. The largest place value that can be subtracted from the decimal one is  $2^0$  or 1. Notice that the  $2^1$  or 2 place column is skipped, so a zero is placed there. However, the  $2^0$  or 1 place value column was used, so a 1 goes there.

Then following step two we subtract, 1-1=0. Now because there is no remainder, the process is finished. Looking at your completed chart, you can see that you've converted decimal 13 to binary  $1101_2$ .

How could you check this answer?

You could check your answer in two ways:

- (a) Add the digit values of the binary number you've jus

derived (8 + 4 + 0 + 1 = 13); this is taken directly

off your chart.

- (b) Look back to 1201c on pages 9 and 10 at the first binary to decimal conversion example you did.

Though this method is easy, one more example is in order before it's your turn. Let's try converting the decimal number 16.75 to its binary equivalent. Step one, find the largest binary place value you can subtract from 16.75, your decimal number. Looking at your chart, you should be able to see that the number you need is 16 (24). Now annotate a 1 in the 24 or 16 place value position.

| 24 | 23 | 2 <sup>2</sup> | 21 | 20 | 2-1 | 2-2 | 2-3  |   |

|----|----|----------------|----|----|-----|-----|------|---|

| 16 | 8  | 4              | 2  | 1  | . 5 | .25 | .125 |   |

| 1  |    |                |    |    |     |     |      | • |

Step two, subtract the selected number; 16.75 - 16 = .75. Step three, go to step one. Looking at what you have left, .75, you should be able to tell that the next place value you can subtract is  $2^{-1}$  or .5. That means you skipped  $2^3$  or 8,  $2^2$  or 4,  $2^1$  or 2, and  $2^0$  or 1. Therefore, a 0 goes in those positions and a 1 goes in the  $2^{-1}$  position.

| 24 | 23 | 2 <sup>2</sup> | 21 | 20 | 2-1 | 2-2 | 2-3  |

|----|----|----------------|----|----|-----|-----|------|

| 16 | 8  | 4              | 2  | 1  | . 5 | .25 | .125 |

| 1  | 0  | 0              | 0  | 0  | 1   |     |      |

Now you are ready for step two. Simple subtraction, .75 - .5 shows that you have .25 as a remainder. Step three tells you that if you have a remainder, go to step one. The next place value you can subtract is  $2^{-2}$  (.25). Annotate your chart.

| 24 | 23 | 22 | 21 | 20 | 2-1 | 2-2 | 2-3  |   |

|----|----|----|----|----|-----|-----|------|---|

| 16 | 8  | 4  | 2  | 1  | .5  | .25 | .125 | _ |

| 1  | 0  | 0  | 0  | 0  | 1   | 1   |      | _ |

Go to step two, .5 - .5 = 0. No step three is needed because there was no remainder. Your binary number then is  $10000.11_2$ . Let's check this answer by using the chart. First find, then add the binary digit values, 16 + 0 + 0 + 0 + 0 + .5 + .25 = 16.75.

b. <u>Practice</u>. Try converting 31.5, 12, and 14. If you need to, use the pull-out chart from 1201c(5) a few pages back to help you as you convert. If your answers don't match the ones shown, reread 1202. Your answers should be as follows:

$$31.5 = 11111.1_2$$

$12 = 1100.0_2$   $14 = 1110.0_2$

Yes, these examples were easy, but it's not the complexity of the problems that's important; it's the application of the principles.

1203. Binary Multiplication, Subtraction, Addition, and Division

Digital equipment performs mathematical operations differently from the way you do using paper and pencil. Digital equipment does all mathematical operations through addition of binary numbers. Done on paper these operations are long and tedious. Thus, the actual machine operations are outside the scope of this course. Nevertheless, you will explore the basic rules for the multiplication, subtraction, addition, and division of binary numbers. This is not a mathematical exercise—these rules will help you to better troubleshoot digital equipment.

Without a knowledge of these rules, perhaps the easiest way to perform these operations is to convert the numbers into decimal, do the operation, then convert the answer back to binary. But once you know the rules you no longer need to perform these extra steps. This knowledge is just as important to you as any tool in your repair kit. Now, in the interest of sharpening your troubleshooting skills, a discussion of the rules of binary mathematical operations follows.

a. <u>Multiplication</u>. Once you know the rules, multiplying binary numbers is easy. These are the rules:

0 x 0 = 0 1 x 0 = 0 0 x 1 = 0 1 x 1 = 1

This multiplication table should look very familiar to you. These values are the same as in the decimal system, so let's go on to the other operations.

b. <u>Subtraction</u>. In binary subtraction, the following basic rules apply:

0 - 0 = 0 1 - 0 = 1 1 - 1 = 0 0 - 1 = 1 borrow 1

(1) These binary subtraction rules also should look familiar, until you get to that last equation, 0 - 1 = 1 borrow 1. Binary subtraction in one instance does require you to borrow from the next highest place value column in order to complete a subtraction. That one instance is 0 - 1, and the rule covering this is 0 - 1 = 1 borrow 1. Now To see what is happening here, look at this decimal example:

40 - 21 =

To solve this problem, you would first attempt to subtract one from zero. But you can't do that, so you borrow from the next highest place value column. In this case, you borrow a ten from the tens place value column.

Now you would be able to subtract one from ten, leaving you a nine in the ones column of your answer. Next you would subtract twenty from what used to be forty--but is now thirty (since you borrowed ten from it)--leaving you a one in the tens column of your answer. Your computations might look something like this:

(2) Now that you've seen the rules and a decimal example of borrowing--let's try two binary examples:

101 100 -<u>11</u> -<u>1</u>

In case you've forgotten binary place values, here's a chart to work with:

$2^4$   $2^3$   $2^2$   $2^1$   $2^0$   $2^{-1}$   $2^{-2}$   $2^{-3}$  16 8 4 2 1 .5 .25 .125

In the first example, the first binary subtraction 101 is one minus one. According to the rules, 1 - 1 = 0. -11

This was done and a zero was placed in the ones

place position of the answer.

The second subtraction of the first example is zero minus one. According to the rules 0 - 1 = 1 borrow 1.

So, borrow one from the next higher place column (four's place or  $2^2$ ) and place a one in the two's column of the answer.

1 191 -<u>11</u>

Let's look at what you did. The digit one you borrowed had a digit value of four. You then subtracted a one with a digit value of two from the one (digit value four) you borrowed. Your answer was a one with a digit value of two. Simply, four minus two equals two.

In the second example, your first binary subtraction 100 is zero minus one (0 - 1).

Again, according to the rules, 0 - 1 = 1 borrow 1, so you attempt to borrow one from the next higher place value (two's place). But because that column has a zero, you have to borrow from the next highest place (four's place).

This done, you place a one in the one's place of your answer and go to the next subtraction.

This subtraction is one minus zero (1-0). The rule for this subtraction is 1-0=1. This done, you place a one in the two's column of your answer. The reason that this second subtraction procedure is one minus zero is because you went two places to borrow the one in your first subtraction. So what you have actually done is taken a four (borrowed a one with a digit value of four) and distributed it between the two's and one's columns. You put two  $(10_2)$  in the one's column so you could make your first subtraction. Because you still had two left over, you put a two (one with a digit value of two) in the two's column. If all the computations were to be shown, it would look like this:

c. Addition. In binary addition, the following basic rules apply:

These rules are also familiar, at least until that last equation, 1 + 1 = 0 carry 1. In the decimal system one plus one equals two; however, that digit doesn't exist in the binary numbering system. A count higher than one means some value must be carried over to the next highest place value. Another decimal example:

$$19 + 21 =$$

To solve this problem you would first add one and nine and get ten. This is fine, but because you can't get ten, (two digits) in one place value column, you put a zero in the ones column of your answer and carry the ten into the ten's place value column. Now add the ten you carried over along with the ten (from the nineteen) and the twenty (from the twenty-one) together to get forty. Lastly, put a four in the ten's column of your answer and go on your merry way. Your computations might look something like this:

A simple binary addition problem to illustrate this concept:

$$1 + 1 =$$

If you follow the rule of 1 + 1 = 0 carry 1, you'd put a zero in the one's column of your answer, and carry 1 over to the two's column. This carry would be brought down into the two's column of your answer. The computation might look something like this:

d. <u>Division</u>. Division in binary is a fairly straightforward process. The following rules for binary division apply:

$$0 + 0 = 0$$

$0 + 1 = 0$

$1 + 1 = 1$

As in binary multiplication, there's nothing new or unusual to report concerning the rules for binary division.

Here's a chart to help you keep those rules straight.

| MULTIPLICATION                                   | SUBTRACTION                                                  | ADDITION                                                    | DIVISION                            |

|--------------------------------------------------|--------------------------------------------------------------|-------------------------------------------------------------|-------------------------------------|

| O x 0 = 0<br>1 x 0 = 0<br>0 x 1 = 0<br>1 x 1 = 1 | 0 - 0 = 0<br>1 - 0 = 1<br>1 - 1 = 0<br>0 - 1 = 1<br>borrow 1 | 0 + 0 = 0<br>0 + 1 = 1<br>1 + 0 = 1<br>1 + 1 = 0<br>carry 1 | 0 + 0 = 0<br>0 + 1 = 0<br>1 + 1 = 1 |

Lesson Summary. This lesson introduced you to binary mathematical operations. You should now have the skill and knowledge to convert between binary and decimal as well as to add, subtract, divide, and multiply binary numbers. These skills are the heart of digital logic.

|         |             | _                                              |           | _    |                    |                          |                  |                  |

|---------|-------------|------------------------------------------------|-----------|------|--------------------|--------------------------|------------------|------------------|

| Exercis | e:          | Complete i required. at the end                | Check yo  | ur r | esponse            | performings<br>s against | g the a<br>those | action<br>listed |

| 1.      | Wha         | t is the de                                    | cimal equ | ival | ent of :           | 1110.1 <sub>2</sub> ?    |                  |                  |

|         |             | 13.5<br>14.5                                   |           |      | 15.1<br>16.125     |                          |                  |                  |

| 2.      | Wha         | at is the decimal equivalent of 10001.012?     |           |      |                    |                          |                  |                  |

|         |             | 14.125<br>16.25                                |           | •••  | 17.25<br>19.25     |                          |                  |                  |

| 3.      | Wha         | t is the binary equivalent of 31.75?           |           |      |                    |                          |                  |                  |

|         | a.<br>b.    | 1111.11 <sub>2</sub><br>11001.011 <sub>2</sub> |           |      | 11110.:<br>11111.: |                          |                  |                  |

| 4.      | Wha         | t is the bi                                    | nary equi | vale | nt of 9            | .125?                    |                  |                  |

|         | a.<br>b.    | 1001.001 <sub>2</sub><br>1010.001 <sub>2</sub> |           |      | 1011.0             |                          |                  |                  |

| 5.      |             | the space p<br>tiplication                     |           | elow | write '            | the rules                | for b            | inary            |

|         |             |                                                |           |      |                    |                          |                  |                  |

|         |             |                                                |           |      |                    |                          |                  |                  |

|         | <del></del> |                                                |           |      |                    |                          |                  |                  |

| 6.      |             | the space p                                    | rovided b | elow | write              | the rules                | for b            | inary            |

|         |             |                                                |           |      |                    |                          |                  |                  |

|         | <del></del> |                                                |           |      |                    |                          |                  |                  |

|         | **********  |                                                |           |      |                    |                          |                  |                  |

| 7. | In the space addition. | provided | below | write | the | rules | for | binary |

|----|------------------------|----------|-------|-------|-----|-------|-----|--------|

|    |                        |          |       |       |     |       |     |        |

|    |                        |          |       |       |     |       |     |        |

### UNIT SUMMARY

By learning the basics of digital logic in this study unit, the binary numbering system, you have mastered the foundation for the following study units. Your next study unit will introduce you to the building blocks of digital logic, logic gates.

### Lesson 1 Exercise Solutions

|    | c.                       | 1101a |

|----|--------------------------|-------|

|    | b.                       | 1101a |

| З. | a.                       | 1101a |

|    | C.                       | 1102b |

|    | base, point, place value | 1101  |

| 6. | binary point             | 1101b |

Reference

### Lesson 2 Exercise Solutions

|    |                      | <u>Reference</u> |

|----|----------------------|------------------|

| 1. | b.                   | 1201             |

| 2. | c.                   | 1201             |

| 3. | d.                   | 1202             |

| 4. | a.                   | 1202             |

| 5. | $0 \times 0 = 0$     | 1203a            |

|    | $1 \times 0 = 0$     |                  |

|    | $0 \times 1 = 0$     |                  |

|    | $1 \times 1 = 1$     |                  |

| 6. | 0 - 0 = 0            | 1203b            |

|    | 1 - 0 = 1            |                  |

|    | 1 - 1 = 0            |                  |

|    | 0 - 1 = 1  borrow  1 |                  |

| 7. | 0 + 0 = 0            | 1203c            |

|    | 0 + 1 = 1            |                  |

|    | 1 + 0 = 1            |                  |

|    | 1 + 1 = 0  carry  1  |                  |

| · |  |  |

|---|--|--|

|   |  |  |

#### STUDY UNIT 2

#### LOGIC OPERATIONS

Introduction. In the previous study unit, you were introduced to the binary numbering system. You will use this knowledge to understand the logic operations and the logic gates that perform these logic operations.

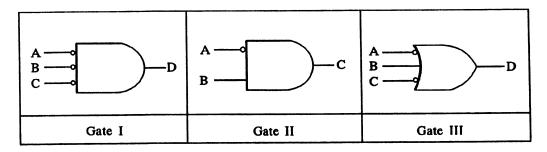

The building blocks of digital electronic circuits are logic gates. Each gate performs a specific logic function. It is the arrangements of these simple gates that determine the difference between a computer and a radio. Understanding these logic gates is essential if you are to successfully repair digital electronic equipment. The gates themselves are few and simple, but the combinations of these simple building blocks may be staggeringly complex. Each type of gate is unique in the function that it performs. This study unit will give you the knowledge to identify these different gates as well as understand their different functions.

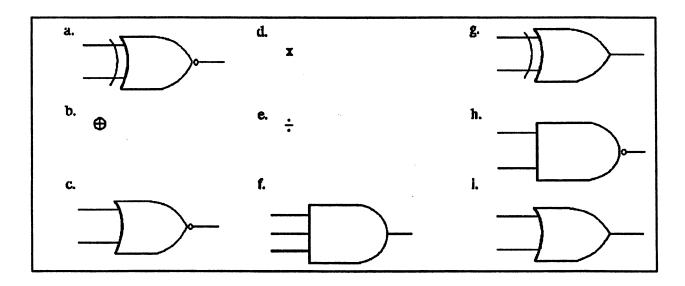

#### Lesson 1. BASIC LOGIC OPERATIONS

#### LEARNING OBJECTIVES

- 1. State in writing the three basic logic operations.

- 2. From a chart of algebraic logic symbols, select the OR symbol.

- From a chart of schematic logic symbols, select an OR symbol.

- 4. Given a labeled OR gate, state in writing the equation describing that gate.

- 5. Given a labeled OR gate, state in writing the truth table derived from that gate.

- 6. From a chart of algebraic logic symbols, select the AND symbol.

- 7. From a chart of schematic logic symbols, select an AND symbol.

- 8. Given a labeled AND gate, state in writing the equation describing that gate.

- 9. Given a labeled AND gate, state in writing the truth table derived from that gate.

## 2101. The Three Basic Logic Operations

There are three basic logic operations: ANDing, ORing, and complementing. These operations both singly and combined form the circuits of digital electronic equipment. The operations are performed by electronic switches known as logic gates. In this lesson, the three basic logic functions will be explained to you.

What are the basic logic operations?

Your answer should have been the following:

ANDing, ORing, and complementing

## 2102. Logic Levels

The electronic switches known as gates may have one or more inputs. Regardless of the number of inputs, these gates will have but one output. There are only two voltage levels associated with these inputs and outputs. The voltage levels found in most digital electronic equipment are five volts and zero volts. These two voltage levels are represented by ones and zeros and are called logic conditions, states, or levels. The more positive voltage is represented by a one, and the more negative voltage is represented by a zero. This set of conditions, where the higher voltage is represented by a one and the lower voltage by a zero, is known as positive logic.

During this lesson you will be using positive logic only. Further, the voltage represented by a one is known as the <u>true</u> condition, the <u>high</u> condition, or the <u>on</u> condition. The voltage represented by the zero is known as the <u>false</u> condition, the <u>low</u> condition, or the <u>off</u> condition. Let's review this important information:

- \* Logic gates are electronic switches that perform electronic logic operations.

- \* Logic gates may have more than one input, but only one output.

- \* Digital electronic equipment uses two voltage levels.

- \* The voltage levels are known as logic levels, logic states, or conditions.

- \* A high, on, true, or a one are associated with the higher voltage. (remember, positive logic only for now)

- \* A low, off, false, or a zero are associated with the lower voltage. (positive logic)

The condition or state of a logic gate is determined by its output level. Logic gates are either on or off, in a true condition or a false condition, in an active state or an inactive state, showing a logic high or a logic low. Again, level, state, and condition all mean the same thing—a description of the voltage level of a particular input or output. But, the logic level of the output of a gate is also a description of the state of that gate. Figure 2-1 summarizes these levels.

| ONE    | ZERO     |

|--------|----------|

| HIGH   | LOW      |

| ON     | OFF      |

| ACTIVE | INACTIVE |

| TRUE   | FALSE    |

Fig 2-1. Logic levels or states.

How is the state of a gate determined?

Right, the level of the output of the gate determines the state of that gate. That is, if the output of a certain gate is a high, then the state or condition of that gate is active, true, on, or high.

Now, let's discuss the actual logic functions and their associated gates.

### 2103. OR Function

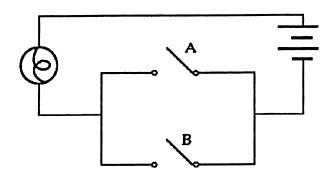

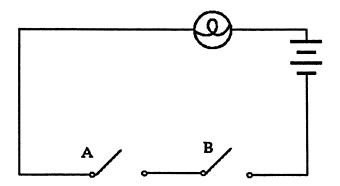

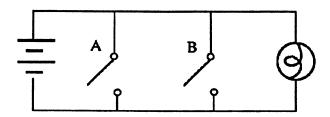

The OR function acts like switches in parallel (fig 2-2).

Fig 2-2. OR Function.

In this circuit the path for current flow is either through switch A <u>or</u> switch B. The OR function states simply that if any or all of its inputs are true, then the output is true. The output is false only when all the inputs are false. This will be explained to you as you complete this lesson.

a. <u>Conditions</u>. The **OR** function is represented algebraically by the + sign. This sign is read as or, not the familiar plus. To represent the **OR** function performed by the switches in figure 2-2, the equation A + B = C can be used. It would be read as A or B equals C. Let's look a little closer at what this equation is actually representing:

If switch A closes, the light will light.

If switch B closes, the light will light.

If both switch A and switch B close, the light will light.

If switch A and switch B are open, the light will not light.

What is the algebraic symbol for the OR function?

If you indicated this symbol +, you're right.

But how is it read?

Yes, this symbol is read--or.

b. <u>Truth table</u>. In digital logic, we let the ones and zeros do the talking. So if you were to go back to the equation (A + B = C) and give values to the variables, you would find only two possibilities for each variable.

Remember: Condition, state, and level have the same meaning. True, on, active, and high are associated with a one, while false, off, inactive, and low are associated with a zero.

(1) If a closed switch were the true condition, the open switch the false condition, and the light being lit the desired true condition--you could compose four equations:

Remember: These equations are read: one or zero equals one; zero or one equals one; one or one equals one; zero or zero equals zero.

The third equation should look strange to you. This is not a misprint. The algebra you have been working with since starting this study unit is called Boolean algebra. Boolean algebra is used to describe the relationships of digital logic. In Boolean algebra the + symbol does not have the same meaning it has in the ordinary algebra, with which you are no doubt more familiar. Here, in Boolean terms the + symbol means a logical sum.

(2) From these four equations, you can derive a truth table. A truth table is simply a summary of the equation with values inserted for the variables for a gate or circuit in chart form. A summary of the previous equation in chart form would look like this:

T = true F = false

| A | В | С |

|---|---|---|

| T | F | Т |

| F | Т | Т |

| T | Т | т |

| F | F | F |

| A | В | С |

|---|---|---|

| 1 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 1 | 1 |

| 0 | 0 | 0 |

These charts are the truth tables for the OR function, with two inputs.

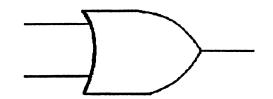

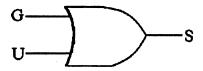

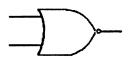

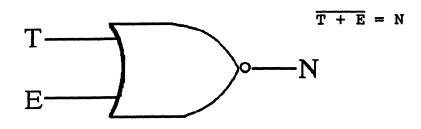

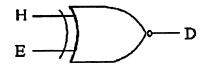

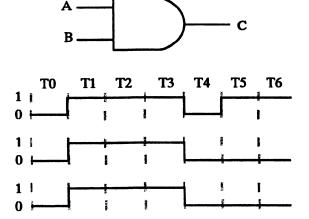

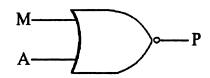

c. <u>Gate</u>. The last thing to learn is the gate itself. To the right is the schematic symbol for an **OR** gate.

Here is a labeled **OR** gate along with its equation and truth table:

A + L = F

| A | L | F |

|---|---|---|

| 1 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 1 | 1 |

| 0 | 0 | 0 |

Now that the gate, equation, and truth table are together, the relationship between the three are easily seen. A or L equals F tells you that F will only be true if A is true or if L is true. The truth table restates this relationship for each of the variables.

| When is this gate active? | The gate is active when the output is true.                       |

|---------------------------|-------------------------------------------------------------------|

| When is the output true?  | The output is true when<br>either input A <u>or</u> L<br>is true. |

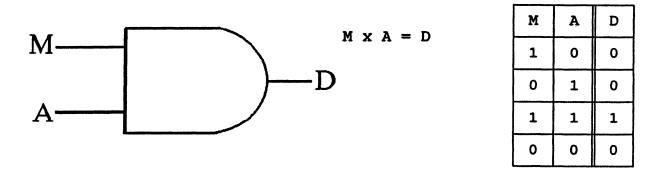

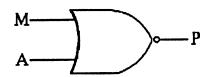

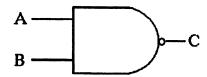

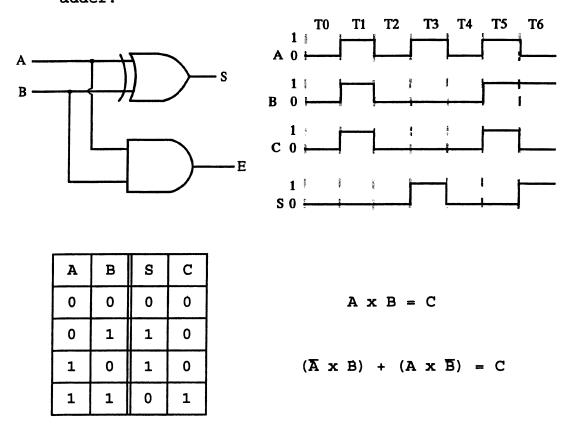

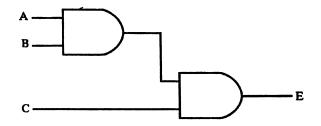

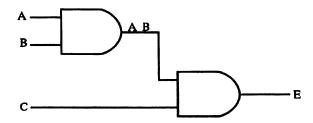

#### 2104. AND Function

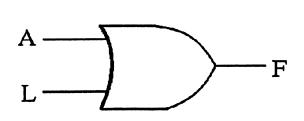

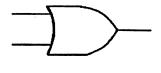

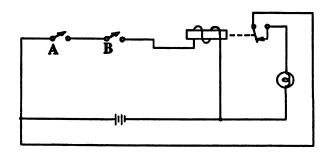

The AND function acts like two switches in series (fig 2-3).

Fig 2-3. AND Function.

In this circuit the path for current flow is through both switch A and switch B. The AND function states that the output will be true only when all inputs are true (or in this case A and B must be true). As you go through this lesson, this concept will become clear to you.

Conditions. This function also has algebraic symbols. The symbols that indicate the AND function include the x symbol, the · symbol, and brackets (). This symbol is read as "and," not multiplied by or times. The AND function is also indicated by an absence of symbols as in this expression: AB = C. algebraically represent the function performed by the circuit above, you could use this equation:  $A \times B = C$ . This is read A and B equals C. Again, a closer look at what this equation represents in this circuit will be helpful:

If switch A alone closes, the light will not light.

If switch B alone closes, the light will not light.

If both switch A and switch B close, the light will light. If both switch A and switch B open, the light will not light.

b. Truth table. You can derive four equations and a truth table from the previous statements describing the circuit in figure 2-3. The four equations would be as follows:

$1 \times 0 = 0$  switch A closed, B open (true, false) 0 x 1 = 0 switch A open, B closed (false, true) 1 x 1 = 1 switch A closed, B closed (true, true)

$0 \times 0 = 0$  switch A open, B open (false, false) The truth tables would be as follows:

T = true F = false C C A В В Α T F F 1 0 0 F F T 0 1 0 Т T Т 1 1 1 F F F 0 0 0

These truth tables describe a two input AND function.

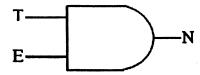

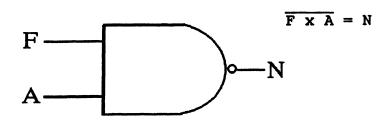

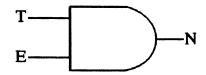

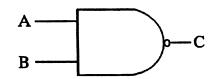

c. <u>Gate</u>. The best is left for last again. This is a labeled **AND** gate, its equation, and truth table.

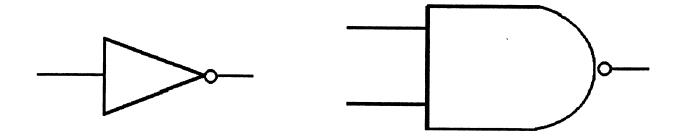

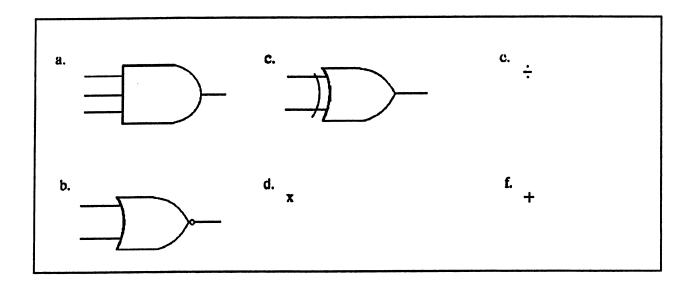

2105. Complementation